# cādence°

# Allegro PCB Design Solution

Managing complexity for faster, more cost-effective implementations

Systems companies are impacted by new devices and design methodologies offered by the semiconductor industry. New devices often bring more challenges, like increasing pin counts packaged in shrinking pin pitch ball grid arrays (BGAs). Additionally, new devices use evolving standards-based interfaces, such as DDR3, DDR4, PCI Express Gen3, USB 3.0, and others, that may require learning new ways to implement them on the board. Coupled with these increasingly complex technologies is the desire by companies to differentiate their offerings and get them to market faster, cheaper, with more functionality and in reduced end product size. As a result, many companies now outsource to or partner with companies in low-cost geographies. To manage such increasing complexities, PCB designers need a solution that addresses their technological and methodological challenges.

### Allegro PCB Design Solution

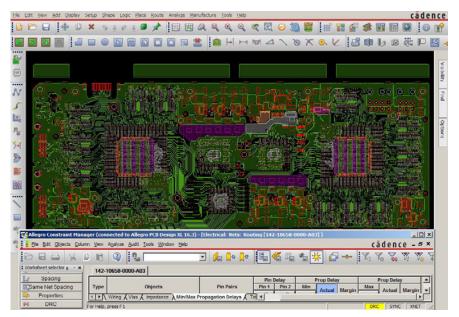

Cadence<sup>®</sup> Allegro<sup>®</sup> PCB Designer is a scalable, proven PCB design environment that addresses technological and methodological challenges while making the design cycles shorter and predictable. Available in base plus options configuration, the PCB design solution contains everything needed to create a PCB layout with a fully integrated design flow. The base-Allegro PCB Designer—includes a common, consistent constraint management solution, PCB Editor, an auto/interactive router, as well as interfaces for manufacturing and mechanical CAD. PCB Editor provides a complete placement and routing environment—from basic floorplanning, placement, and routing to placement replication and advanced interconnect planning—for simple to complex PCB designs.

# Benefits

• Offers a proven, scalable, cost-effective PCB editing and routing solution in on-demand base plus options configuration

- Eliminates unnecessary iterations through constraint-driven PCB design flow

- Supports a comprehensive rule set for physical, spacing, design for fabrication (DFF), design for assembly (DFA), and design for test (DFT), high-density interconnect (HDI), and electrical (high-speed) domains

- Features a common, consistent constraint-management system for creation, management, and validation of constraints from front to back

- Open environment for third-party application improves productivity while providing access to best-ofbreed integrated point tools

# **PCB Editor Technology**

#### Constraint-Driven PCB Editing Environment

At the heart of Allegro PCB Designer is a PCB Editor—an intuitive, easy-to-use, constraint-driven environment for creating and editing simple to complex PCBs. Its extensive feature set addresses a wide range of design and manufacturability challenges:

- A powerful set of floorplanning and placement tools including placement replication for accelerating placement of the design

- Powerful shape-based shove, hug interactive etch creation, editing establishes a highly productive interconnect environment while providing real-time, heads-up displays of length and timing margins

- Dynamic shape capability offers real-time copper pour plowing and healing functionality during placement and routing iterations

The PCB Editor can also generate a full suite of phototooling, bare-board fabrication, and test outputs, including Gerber 274x, NC drill, and bare-board test in a variety of formats.

#### **Constraint Management**

A constraint management system displays physical/spacing and high-speed rules along with their status (based on the current state of the design) in real time and is available at all stages of the design process. Each worksheet provides a spreadsheet interface that enables users to define, manage, and validate the different rules in a hierarchical fashion. With this powerful application, designers can graphically create, edit, and review constraint sets as graphical topologies that act as electronic blueprints of an ideal implementation strategy. Once they exist in the database, constraints can drive the placement and routing processes for constrained signals.

The constraint management system is completely integrated with the PCB Editor, and constraints can be validated in real time as the design process proceeds. The result of the validation process is a graphi-

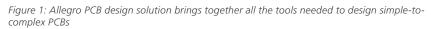

Figure 2: DFA rules-driven placement allows for compact placement of components without introducing errors

cal representation of whether constraints pass (highlighted in green) or fail (highlighted in red). This approach allows designers to immediately see the progress of the design in the spreadsheets, as well as the impact of any design changes.

#### Floorplanning and Placement

The constraint and rules-driven methodology of PCB design solutions includes a powerful and flexible set of placement capabilities, including interactive and automatic. The engineer or designer can assign components or subcircuits to specific "rooms" during design entry or floor- planning. Components can be filtered and selected by reference designator, device package/footprint style, associated net name, part number, or the schematic sheet/page number.

With thousands of components comprising today's boards, precise management is critical. Real-time assembly analysis and feedback can facilitate this management—helping designers increase productivity and efficiency by placing components according to corporate or EMS guidelines. Dynamic DFA-driven placement offers real-time packageto-package clearance checking during interactive component placement (see Figure 2). Driven from a two-dimensional spreadsheet array of classes and package instances, real-time feedback provides minimum clearance requirements. Based on the package's side-to-side, side-toend, designers can simultaneously place devices for optimum routability, manufacturability, and signal timing.

#### **Placement Replication**

Superior placement replication technology within Allegro PCB Designer allows users to quickly place and route multiple similar circuits in a design. It allows users to create a template using one instance of placed and routed circuit that can be applied to other instances within the design. The saved placement template can be used with other designs where similar circuits are used. When replicating placement, users can flip or mirror the circuit from top layer to bottom layer. All associated etch elements, including blind buried vias, are mapped to correct layers when circuit is moved from top layer to bottom layer.

#### **Display and Visualization**

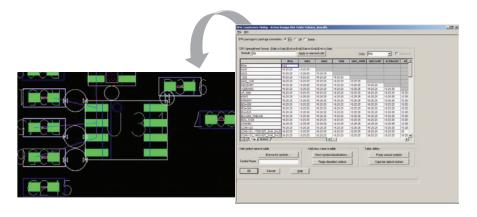

The built-in 3D viewer is available in all PCB Editor products. The 3D environment supports several filtering options, camera views, graphic display options such as solid, transparency, and wireframe, and mouse-driven controls for pan, zoom, and spinning the display. 3D viewing also supports the display of complex via structures or isolated sections of the board. Multiple display windows can be opened using the context sensitive command structure, and 3D images can be captured and saved in JPEG format. (See Figure 3.)

The flipboard capability "flips" the design about its Y axis inverting the design database in the canvas. This "flip" reorganizes the display of the design such that what was displayed as top through to bottom becomes bottom through to top. Having a true bottom side view from within the CAD system is essential for hardware

Figure 3: Built-in 3D viewer allows reviewing of a section of the board or complex via structures with pan, zoom, rotation, and spinning to reduce iterations with mechanical design teams or PCB fabricators without introducing errors

engineers when debugging a board in the lab, or for assembly/test engineers on the manufacturing floor. Flipboard is not just limited to viewing; design edits can also be performed while in this mode.

#### Interactive Etch Editing

The routing feature of the PCB Editor provides powerful, interactive capabilities that deliver controlled automation to maintain user control, while maximizing routing productivity. Real-time, shapebased, any-angle, push/shove routing enables users to choose from "shovepreferred," "hug-preferred," or "hugonly" modes.

During etch editing, the designer can view a real-time, graphical heads-up display of how much timing slack remains for interconnect that has high-speed constraints. Interactive routing also enables group routing on multiple nets and interactive tuning of nets with high-speed length or delay constraints.

#### **Multi-Line Routing**

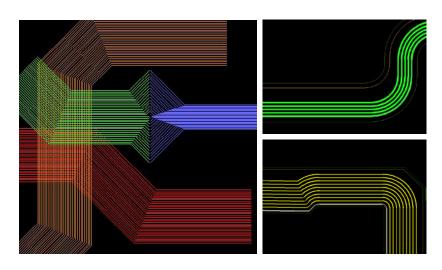

Multi-line routing allows users to quickly route multiple lines as a group on the PCB. Coupled with "hug-contour" option, this utility can help designers route multiple lines on the flex portion of the rigid-flex design in minutes instead of hours with traditional one trace at a time. Hug-contour option takes care of inserting traces with curves that are aligned to contour of the flex portion of the design. (See Figure 4.)

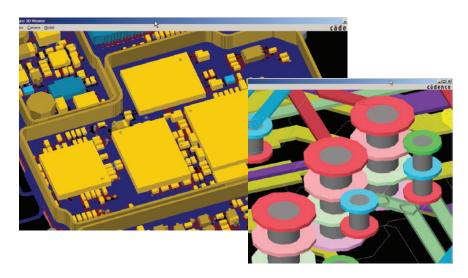

#### **Design Planning and Routing**

Highly constrained, high-density designs dominated by bussed interconnect can take significant time to strategically plan and route. Compound this with the density issues of today's components, new signaling levels, and specific topology requirements—and it's no wonder that traditional CAD tools and technologies fall short of capturing a designer's specific routing intent and acting upon it. The Allegro Interconnect Flow Planner provides the technology and methodology to capture as well as adhere to a designer's intent. Through the interconnect flow planning architecture and the global route engine, users can for the first time put their experience and design intent into a tool that understands what they want—natively.

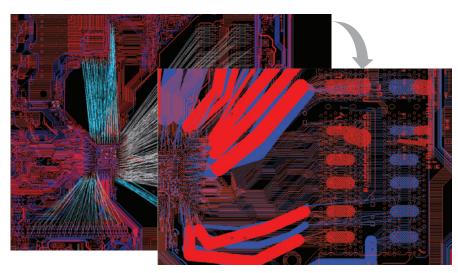

Users create abstracted interconnect data (through the interconnect flow planning architecture) and can quickly converge on a solution and validate it with the global route engine. The interconnect abstraction reduces the number of elements the system has to deal with—from potentially tens of thousands down to hundreds resulting in a significant reduction in the manual interaction required.

Using the abstracted data, the planning and routing process can be accelerated by providing a visual/spatial map of the open area in relation to the data and the user's design intent. The route engine can then deal with the details of the routing, adhering to the specified intent, without the user having to both visualize and solve the interconnect problems at once. This significant simplification over current design tools means users converge on a

Figure 4: Multi-line routing with contour hug option accelerates through no-click routing on flex section of the PCB designs

Figure 5: Allegro Interconnect Flow Planner technology allows users reduce layer counts and shorten design cycle through design planning

successful interconnect solution far faster and more easily than ever before, reducing design cycle time through increased efficiency and productivity. (See Figure 5.)

Getting routes out of dense BGAs is increasingly difficult for PCB designers. With increasing pin counts and shrinking pin pitches, the time PCB designers spend on getting routes in and out of BGAs has gone up significantly. The traditional approach of performing breakouts first then routing the traces between two BGAs is running out of steam because resolving the resulting crossovers takes up a lot of time and board real estate.

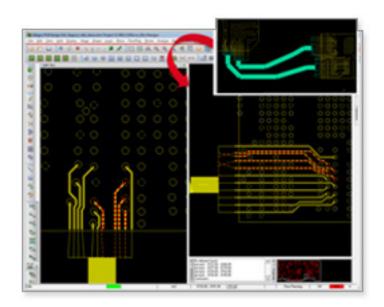

#### Aibt

Auto-interactive Breakout Technology (AiBT) improves user efficiency by allowing users to plan to break out on both ends. AiBT can be used with the new, Split View, and Bundle Sequence commands to dramatically shorten the time required to develop a high-quality and properly ordered breakout solution (see Figure 6).

#### **High-Speed Design**

Increasing use of standards-based advanced interfaces such as DDR3, DDR4, PCI Express, USB 3.0 are bringing a set of constraints that must be adhered to while implementing a PCB.

Allegro PCB Designer through its High-Speed Option makes adhering to constraints on advanced interfaces quick and easy. It offers an extensive range of electrical rules to ensure that the PCB design implementation is complaint with the specification for advanced interfaces. Additionally, it allows users to extend the rules through the use of formulas with existing rules or post-route data such as actual trace lengths.

The PCB High Speed Option allows users to apply a topology to a set of signals. A topology can include a set of routing preferences as well as constraints such as putting the termination resistor closer to either the driver or a receiver on a signal. The constraint-driven PCB design system then provides feedback through the constraint manager if a signal doesn't conform to the topology or the rules associated with the topology, ensuring that issues are identified (and therefore can be addressed) as quickly as possible.

Allegro PCB High Speed Option also enables checking of delays through vias, connector pins, and IC packagepin for die 2 die length/delay matching. It includes, utilities to identify trace segments crossing voids (return path issues that cause re-spins), supports back drilling (remove through hole antennas) as well as provides a Timing Environment that can accelerate timing closure of critical nets up to 60-70%.

#### Accelerated Timing Closure

As the data rates increase and supply voltages decrease in today's advanced interfaces like DDR3/DDR4, PCI Express, SATA, etc., PCB designers must spend more time to ensure signals in an interface meet timing requirements. With increasing density on PCBs, the effort to get to timing closure—ensuring all signals meet timing requirements—can increase significantly. PCB designers need new tools to meet this increasingly complex challenge.

Figure 6: Split View allows working on both ends of a zoomed-in interface

Figure 7: AiDT shortens time to tune high-speed signals by 50% or more.

#### **Timing Vision**

Timing Vision is an innovative and unique environment that allows users to graphically see real-time delay and phase information directly on the routing canvas. Traditionally, evaluating current status of timing/length of a routed interface requires numerous trips to Constraint Manager and/or use of the Show Element command. Using an embedded route engine to evaluate complex timing constraints and interdependencies amongst signals shows current status of a set of routed signals—a DDRx byte lane or a complete DDRx interface via custom trace/connect line coloring; stipple patterns and customized data tip information to define the delay problem in the simplest terms possible.

With the embedded route engine, Timing Vision provides real-time feedback to the user during interactive editing and enhances the user's ability to develop a strategy for resolving timing on large buses or interfaces such as DDRx, PCI Express, etc. Coupled with Auto-interactive Phase Tuning (AiPT) and Auto-interactive Delay Tuning (AiDT) capabilities, users can accelerate the time to tune advanced interfaces like DDRx in one-third the time it takes to do it manually using traditional methods.

#### AiPT

Differential pairs in an interface like DDRx require designers to match static as well as dynamic phase. Matching phase for all differential pairs in an interface is a necessary first step before tuning and matching the rest of the signals. AiPT automatically matches dynamic and static phase for the selected differential pairs. It works with a set of parameters that allows the user several options for trace lengthening or shortening as well as pad entry/exit options. With AiPT, users can significantly shorten the time to match static and dynamic phases for differential pairs.

#### AiDT

Delay tuning for signals for interfaces like DDRx takes up too much time when using traditional, manual methods. AiDT automatically generates tuning patterns on a user-selected routed byte lane or interface based on user-defined timing constraints and tuning parameters. AiDT computes the required length for the connections to meet timing constraints and utilizes controlled push/shove techniques when adding tuning patterns (see Figure 7).

#### Backdrilling

Allegro PCB High-Speed Option allows users to specify which vias on critical high-speed signals should be back drilled to avoid reflections. An output report— Backdrill NC and Legend Files from Bottom, Top, or Any Layer if backdrilling the inner core(s) of the PCB—allows users to send backdrilling instructions to their PCB manufacturers

# Design for Manufacturing

Allegro PCB Editor supports DFT, DFF, and DFA checks during the design implementation process. Users can select the number and type of probe points and pad sizes as well as define no-probe areas and create reports to check testability coverage. Allegro PCB Editor provides a real-time DFA design rules check as components are being placed with visual feedback while the component is on the cursor.

#### Design Data Transfer to Manufacturing

A full suite of phototooling, bare-board fabrication, and test outputs, including Gerber 274x, NC drill, and bare-board test in a variety of formats, can be generated. More importantly, Cadence supports the industry initiative toward Gerber-less manufacturing through export and import of design data in IPC-2581 format. The IPC-2581 data is passed in a single file that creates accurate and reliable manufacturing data for high-quality manufacturing. Users have a choice to export a subset of the design data for protecting their IP. Import of IPC-2581 is intended for overlaying artwork data on the design for viewing purposes only.

# Miniaturization

#### Constraint-Driven HDI Design Flow

With BGA pin pitches decreasing to below 1mm, (0.8mm or lower with 0.65mm or 0.5mm pin pitches), users are forced to implement a buildup PCB technology using HDI. While miniaturization is not necessarily the primary objective in many market segments, the move to buildup technology is necessary for fanning out a BGA particularly if it has three or four rows of pins on each side.

The Allegro PCB Designer through its Miniaturization Option offers a proven constraint-driven HDI design flow with a comprehensive set of design rules for all different styles of HDI designs, from a hybrid buildup/core combination to a complete buildup process like ALIVH.

In addition, it includes automation for adding HDI to shorten the time to create designs that are correct by construction.

#### **Embedded Components**

Reducing end product size can be accomplished in many different ways. One of the approaches PCB designers are taking is to embed packaged components on inner layers. Allegro PCB Designer through its Miniaturization Option offers constraintdriven embedded component placement and routing. It supports direct- and indirect-attach techniques, and supports embedding components with dual-sided contacts, vertical components, and embedding in dielectric on a two-layer PCB. Additionally it offers the ability to create and manage cavities on layers specified for embedding components.

#### Analog/RF Design

The Allegro PCB Designer through its Analog/RF Design Option offers a mixedsignal design environment, from schematic to layout with back annotation, proven to increase RF design productivity up to 50%. It allows engineers to create, integrate, and update analog/ RF/ microwave circuits with digital/analog circuits in the Allegro PCB Design environment. With its rich layout capability and powerful interfaces with RF simulation tools, it allows engineers to start RF design from Allegro Design Authoring, Allegro PCB Designer, or Agilent ADS.

### **Concurrent Team Design**

Globally dispersed design teams are on the rise, which compounds the challenge of shortening design cycle times. Manual workarounds that address multi-user issues are time-consuming, slow, and prone to error.

Allegro PCB Design Partitioning technology provides a multi-user, concurrent design methodology for faster time to market and reduced layout time. Multiple designers working concurrently on a layout share access to a single database, regardless of team proximity. Designers can partition designs into multiple sections or areas for layout and editing by several design team members. Designs can be partitioned vertically (sections) with soft boundaries or horizontally (layers). As a result, each designer can see all partitioned sections and update the design view for monitoring the status and progress of other users' sections. Such partitioning can dramatically reduce overall design cycles and accelerate the design process.

#### PCB Autorouter Technology

PCB routing technologies are tightly integrated with the PCB Editor. Through the PCB Router interface, all design information and constraints are automatically passed from the PCB Editor. Once the route is completed, all route information is automatically passed back to the PCB Editor.

Increased design complexity, density, and high-speed routing constraints make manual routing of PCBs difficult and time-consuming. The challenges inherent in complex interconnect routing are best addressed with powerful, automated technology. The robust, productionproven autorouter includes a batch routing mode with extensive user-defined routing strategy control as well as built-in automatic strategy capabilities.

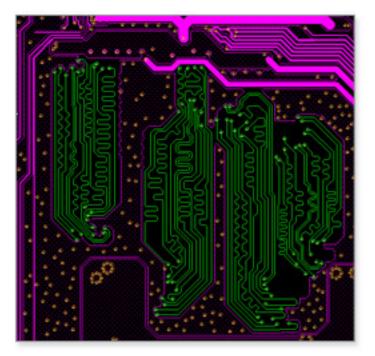

#### DFM Rules-Driven Autorouting

The design for manufacturing capability within Allegro PCB Router significantly improves manufacturing yields. Manufacturing algorithms provide a spreading capability that automatically increases conductor clearances on a space-available basis. Automatic conductor spreading helps improve manufactuability by repositioning conductors to create extra space between conductors and pins, conductors and SMD pads, and adjacent conductor segments. Users gain the flexibility to define a range of spacing values or to use the default values.

Mitered corners and test points can be added throughout the routing process. The manufacturing algorithms automatically use the optimal setback range, starting from the largest to the smallest value. Test point insertion automatically adds testable vias or pads as test points. Testable vias can be probed on the front. back, or both sides of the PCB, supporting both single side and clamshell testers. Designers have the flexibility to select the test point insertion methodology that conforms to their manufacturing requirements. Test points can be "fixed" to avoid costly test fixture modifications. Test point constraints include test probe surfaces, via sizes, via grids, and minimum center-tocenter distance.

# High-Speed Constraints-Driven Autorouting

High-speed routing constraints and algorithms handle differential pairs, net scheduling, timing, crosstalk, layer set routing, and the special geometry requirements demanded by today's high-speed circuits. The autorouting algorithms intelligently handle routing around or through vias, and automatically conform to defined length or timing criteria. Automatic net shielding is used to reduce noise on noisesensitive nets. Separate design rules may be applied to different regions of the design; for example, you can specify tight clearance rules in the connector area of a design and less stringent rules elsewhere.

#### **Operating System Support**

#### Allegro Platform Technology:

- Sun Solaris

- Linux

- IBM AIX

- Windows

#### OrCAD Technology:

• Windows

# Allegro PCB Designer Base Plus Options Features

| Feature                                                                | Allegro PCB Designer   |

|------------------------------------------------------------------------|------------------------|

| Allegro Design Authoring                                               | •                      |

| Allegro Design Entry CIS                                               | •                      |

| Constraint Manager: Physical, spacing, and samenet rules               | •                      |

| Constraint Manager: Properties and DRCs                                | •                      |

| Constraint Manager: Differential pair rules                            | •                      |

| Constraint Manager: Region rules                                       | •                      |

| Floorplanning, placement, placement replication                        | •                      |

| DFA, DFF, DFT                                                          | •                      |

| Dynamic feedback on DFA compliance during placement                    | •                      |

| DF3.0, DXF in/out                                                      | •                      |

| EDMD schema-based ECAD-MCAD co-design                                  | •                      |

| Native 3D viewer                                                       | •                      |

| Hierarchical interconnect flow planning                                | •                      |

| Length-based rules for high-speed signals                              | •                      |

| Constraint-driven flow for length-based high-speed signals             | •                      |

| Match groups, layer sets, extended nets                                | •                      |

| T-point rules (pin to T-point)                                         | •                      |

| 6-layer automatic shape-based autorouter                               | •                      |

| High-speed rules-based autorouting                                     | •                      |

| _ayer-specific rules-based autorouting                                 | •                      |

| Design planning - plan spatial feasibility analysis and feedback       | Design Planning Option |

| Design planning - generate topological plan                            | Design Planning Option |

| Design planning - Convert topological plan to traces (CLINES)          | Design Planning Option |

| Auto-interactive Delay Tuning                                          | PCB High-Speed Option  |

| Constraint Manager: Electrical rule set (relection, timing, crosstalk) | PCB High-Speed Option  |

| Constraint-driven flow using electrical rules                          | PCB High-Speed Option  |

| Electrical constraint rule set (ECSets) / topology apply               | PCB High-Speed Option  |

| Formula and relationship-based (advanced) constraints                  | PCB High-Speed Option  |

| Backdrilling                                                           | PCB High-Speed Option  |

| Die2Die pin delay, dynamic phase control, Z-axis delay                 | PCB High-Speed Option  |

| Return path management for critical signals                            | PCB High-Speed Option  |

| Constraint Manager: HDI rule set                                       | Miniaturization Option |

| Vicro-via and associated spacing, stacking, and via-in-pad rules       | Miniaturization Option |

| Constraint-driven HDI design flow                                      | Miniaturization Option |

| Manufacturing rule support for embedding components                    | Miniaturization Option |

| Embedd components on inner layers                                      | Miniaturization Option |

| HDI micro-via stack editing                                            | Miniaturization Option |

| Dynamic shape-based filleting, line fattening, and trace filleting     | Miniaturization Option |

| Hug contour routing (Flex)                                             | Miniaturization Option |

| Support for cavities on inner layers                                   | Miniaturization Option |

| Concurrent team design - layer-by-layer partitioning                   | PCB Team Design Option |

| Concurrent team design - functional block partitioning                 | PCB Team Design Option |

| Concurrent team design - team design dashboard                         | PCB Team Design Option |

| Concurrent team design - soft nets                                     | PCB Team Design Option |

| Edit constraints in a partition                                        | PCB Team Design Option |

| Manage netclasses in a partition                                       | PCB Team Design Option |

| Parameterized RF etch elements editing                                 | PCB Analog / RF Option |

| Asymmetrical clearances                                                | PCB Analog / RF Option |

| Bi-directional interface with Agilent ADS                              | PCB Analog / RF Option |

| Feature                                   | Allegro PCB Designer   |

|-------------------------------------------|------------------------|

| Import Agilent ADS schematics into DE-HDL | PCB Analog / RF Option |

| Layout-driven RF design creation          | PCB Analog / RF Option |

| Flexible Shape Editor                     | PCB Analog / RF Option |

| 256-layer autorouting                     | PCB Routing Option     |

| DFM rules-based autorouting               | PCB Routing Option     |

| Automatic trace spreadiing                | PCB Routing Option     |

| ATP generation                            | PCB Routing Option     |

| Layer-specific rules-based autorouting    | PCB Routing Option     |

#### **Cadence Services and Support**

- Cadence application engineers can answer your technical questions by telephone, email, or Internet—they can also provide technical assistance and custom training

- Cadence certified instructors teach more than 70 courses and bring their real-world experience into the classroom

- More than 25 Internet Learning Series (iLS) online courses allow you the flexibility of training at your own computer via the Internet

- Cadence Online Support gives you 24x7 online access to a knowledge base of the latest solutions, technical documentation, software downloads, and more

#### For More Information

For product sales, support, or additional information on Allegro solutions, visit www.cadence.com/contact\_us to locate a Cadence Sales office or channel partner in your area.

Cadence Design Systems enables global electronic design innovation and plays an essential role in the creation of today's electronics. Customers use Cadence software, hardware, IP, and expertise to design and verify today's mobile, cloud, and connectivity applications. www.cadence.com

©2014 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, and Allegro are registered trademarks of Cadence Design Systems, Inc., All rights reserved. 2106 02/14 SA/DM/PDF